- info@advinno.com

- 周一至周五:上午 9:00 至下午 6:00

LVDS

LVDS

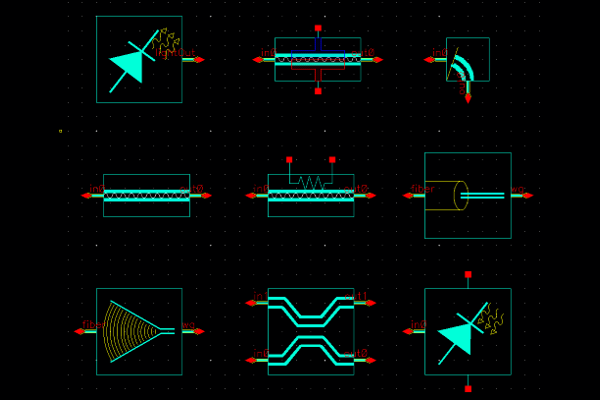

Silicon Creations offers bi-directional LVDS technology implemented across multiple process nodes from 90nm CMOS through 16/12nm FinFET with 7nm FinFET tape-outs. Their portfolio covers multiple uni-directional and bi-directional parallel source-synchronous interfaces for chip-to-chip and video data transmission.

Supporting TIA/EIA644A LVDS and sub-LVDS standards with receiver compatibility for LVPECL, the solutions deliver data rates exceeding 2Gbps with trimmable on-die termination, independent LVCMOS functions, and flexible programmability for FPDLink, FastLVDS, miniLVDS, Camera Link, and OpenLDI standards.

Key LVDS Solutions:

- TIA/EIA644A LVDS and sub-LVDS compatible

- Receiver compatible with LVPECL

- Data rates exceeding 2Gbps

- Trimmable on-die termination

- Independent LVCMOS input and output functions

- FPDLink, FastLVDS, miniLVDS support

- Camera Link and OpenLDI support

- Available 90nm to 7nm FinFET

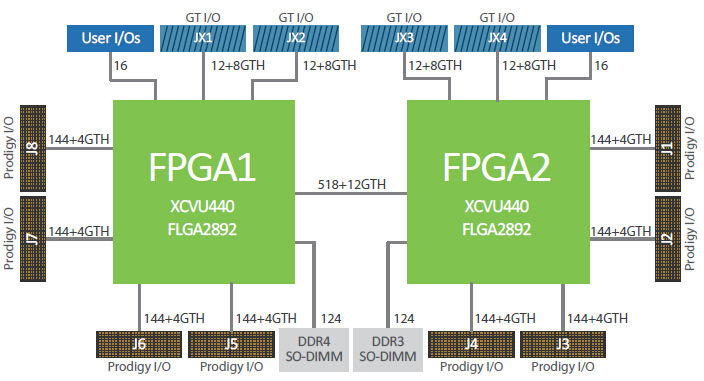

LVDS Interface Architecture

Silicon Creations LVDS provides bi-directional interfaces compatible with TIA/EIA644A LVDS and sub-LVDS standards, with receiver compatibility for LVPECL. Trimmable on-die termination operates during Tx operation and independent LVCMOS functions provide design flexibility.

- TIA/EIA644A LVDS and sub-LVDS compatibility

- LVPECL receiver compatibility

- Trimmable on-die termination during Tx

- Independent LVCMOS input and output functions

High-Speed LVDS Performance

Achieving data rates exceeding 190Mpixels/s (1.34Gb/s per lane) for FPD-link and up to 3.3Gbps per lane in certain configurations, the Silicon Creations FastLVDS receiver delivers over 60% data valid window opening at 1.35Gbps.

- Exceeds 190Mpixels/s (1.34Gb/s per lane) for FPD-link

- Up to 3.3Gbps per lane configurations

- Over 60% data valid window at 1.35Gbps

- Excellent signal integrity across configurations

LVDS Applications

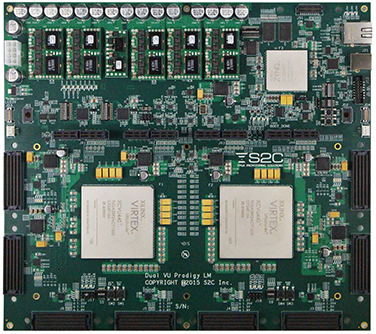

Designed for chip-to-chip communication, video data transmission, FPGA to ASIC conversions, and camera interfaces. Supporting established standards including FPDLink, FastLVDS, miniLVDS, Camera Link, and OpenLDI across process nodes from 90nm through 7nm FinFET.

- FPGA to ASIC conversion support

- Chip-to-chip and video transmission

- Camera Link, OpenLDI, and FPDLink support

- Process nodes from 90nm to 7nm FinFET