- info@advinno.com

- 周一至周五:上午 9:00 至下午 6:00

职业机会

- Home

- 职业机会

Join Our Team

We have ongoing opportunities for enthusiastic and motivated individuals who have the experience, skills, and drive to join our team and help propel us forward.

Please check the current job opportunities below that are open for application.

Please send your Resume to hr@advinno.com.

Job Openings

Job Description:

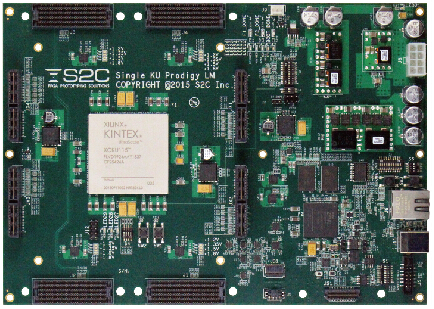

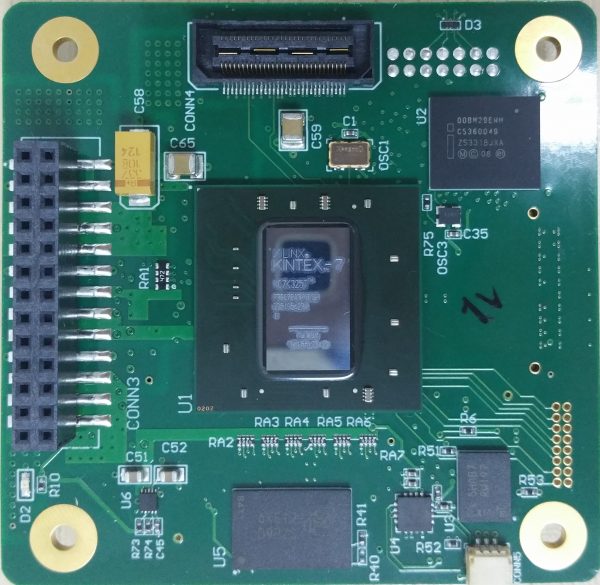

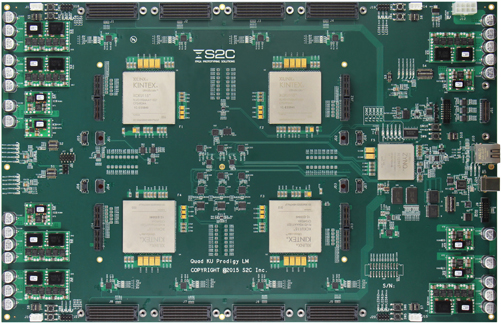

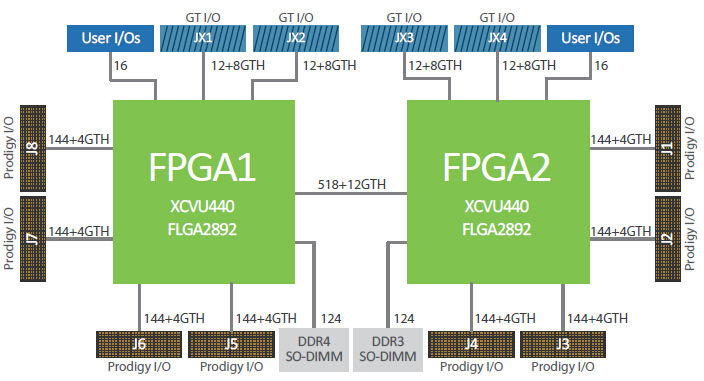

- Design and development of ASIC, FPGA, PCB and Embedded based systems.

- Expert level in Verilog/VHDL/System Verilog/UVM

- Experience in firmware or software application development with C or C++

- Experience with ML, deep learning, PyTorch, TensorFlow, Python, NLP

- Design verification and synthesis of AI/ASIC/FPGA chips

- Involve in System Architectural definition, hardware/software system integration, testing and troubleshooting

- Participate in new products definition and design

- Provide technical support to customers

Job Requirements:

- Candidate should possess a bachelor’s or master’s degree in the field of Electrical or Electronics Engineering, Computer Science or equivalent.

- At least 3 years of experience in ASIC/FPGA/Embedded system design.

- In-depth knowledge and expertise in VHDL, Verilog, System-Verilog, UVM, C and C++

- Well versed of ASIC/Xilinx/Altera design flow.

- Familiar with UNIX/Linux environment and scripting.

- Self-motivated, creative, resourceful, strong analytical and troubleshooting skills.

- Should be able to work independently, has a good team spirit, a strong sense of responsibility, a creative problem solver and be easy to get along with others.

Job Description:

- Responsible for IP level and/or SOC level verification.

- Develop verification plan for complex digital IP from design spec, work closely with design engineers to identify important verification scenarios.

- Create verification environment/testbench with Bus Functional Model (BFM) using SystemVerilog, UVM and/or System C.

- Identify and implement functional coverage and SystemVerilog Assertions to catch functional bugs and to boost design quality prior to tape-out.

- Develop directed/use case/random test cases using SystemVerilog, analyse test results, debug tests and improve verification quality.

- Knowing to use Formal verification with SystemVerilog Assertion (SVA) to verify IP block is a plus.

Requirements:

- Bachelor/Master’s degree in Electrical & Electronics/Computer Engineering or equivalent.

- Familiar with AMBA bus protocol (AXI, CHI, ACE, APB).

- Experience with verification methodology such as SystemVerilog, OVM, UVM, SystemC.

- Experience with functional coverage/SVA assertions and test sequence/case writing.

- Experience with the full verification execution cycle.

- Experience in developing measurable verification plan.

- Experience with function verification for common SoC building blocks and verification IP for NOC/Interconnect/Fabric/PCIE, etc. are added advantages.

- Strong problem solver, communicator and team player.

- Scripting skills in Perl, Python, TCL, shell, etc.

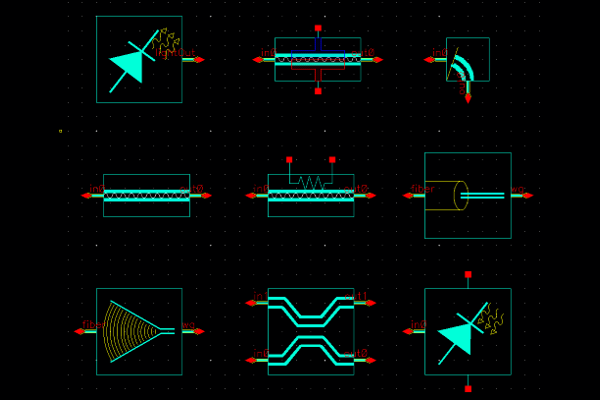

Job Description:

- Work with IC Design engineer to design and layout custom RF, analog and mixed-signal circuits from sub-blocks to top-level integration and verification.

- Perform physical design verifications (LVS/DRC/ERC).

- Collaborate with IC Design engineers to optimize layout implementation for better power, performance, and area.

- Responsible for full-chip physical verification sign-off and tape out.

- Good understanding of semiconductor and circuit design.

Job Requirements:

- Bachelor degree in Electrical and Electronics Engineering or equivalent.

- At least three (5+) or more years of RF, analog /mixed custom layout design experience.

- Experience with schematic-driven layout, floor planning, chip level routing, design rule and physical verification and chip integration.

- Good understanding of critical device matching, high voltage layout techniques, advance node Pmos/ Nmos guarding.

- Good knowledge of design manual.

- Good Knowledge of CAD tools (Cadence Virtuoso, Mentor Calibre DRC/LVS/ERC, Synopsys Hercules, Cadence PVS ).

- Must have good analysis and trouble shooting skills.

- Should be able to work independently, self-motivated, has a good team spirit, a strong sense of responsibility and urgency, a creative problem solver and hardworking.

- Good communication skills in written and verbal English.