- info@advinno.com

- 周一至周五:上午 9:00 至下午 6:00

Modelsim HDL 仿真

- Home

- 产品

- Uncategorized

- Modelsim HDL 仿真

Modelsim HDL 仿真

Modelsim HDL Simulation, now evolved into Questa One Sim, is the industry-leading functional simulation platform for ASIC, SoC, and FPGA designs. It delivers three core benefits: faster engines, faster engineers, and fewer workloads, enabling teams to complete verification tasks with significantly reduced resource demands.

Questa One Sim merges advanced verification workflow capabilities into a single environment, combining high-performance simulation with advanced debug, portable stimulus, and coverage-driven regression tools to accelerate time-to-market for complex chip designs.

Key Modelsim HDL Simulation Solutions:

- Fastest simulation engine for DFT patterns

- RTL and gate-level simulation

- ParallelSim with auto-partitioning

- VHDL constraint solver support

- Advanced X debug with patented technology

- SmartCompile for 3DIC and AI designs

- Multi-test profiler for regression analysis

- Built-in PSS engine for UVM sequences

Built-in PSS Capabilities

Portable Stimulus capability enables reusable test scenarios across multiple platforms and abstraction levels, specifying intent once to generate diverse test cases while reducing redundancy and human error.

- Reusable test scenarios across platforms

- Single intent specification for diverse test cases

- Reduces redundancy and human error

- Supports multiple abstraction levels

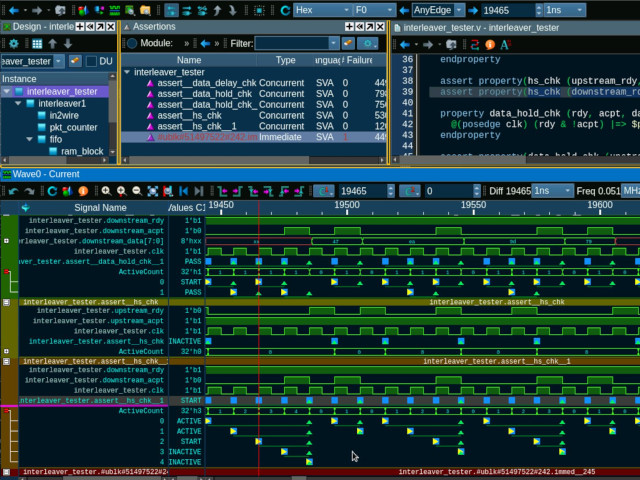

Enhanced Debugging Capabilities

Integrated simulation and debugging engine with a new interface for efficient verification flow, including dedicated debug windows for X-debug, constraints debug, and protocol-aware debug, plus a multi-test profiler for regression-wide analysis.

- Dedicated X-debug and constraints debug windows

- Protocol-aware debug environment

- Multi-test profiler for regression-wide insights

- Advanced debug interface for faster root-cause analysis

CDC Metastability Injection

Works with Questa CDC to dynamically inject metastability into RTL functional simulation, verifying DUT tolerance of random delays while enabling significantly more simulations with metastability injection enabled.

- Dynamic metastability injection into RTL simulation

- Verifies DUT tolerance of random delays

- Significantly more simulations with injection enabled

- Integration with Questa CDC flow