- info@advinno.com

- Mon - Fri: 9.00 am - 6.00 pm

We are creative, ambitious and ready for challenges! Hire Us

We are creative, ambitious and ready for challenges! Hire Us

We have 20+ years of experience in delivering superior and innovative products

22, Sin Ming Lane, #05-75 Midview City Singapore 573969

info@advinno.com

(+65) 6777-2240 / 6570 6086

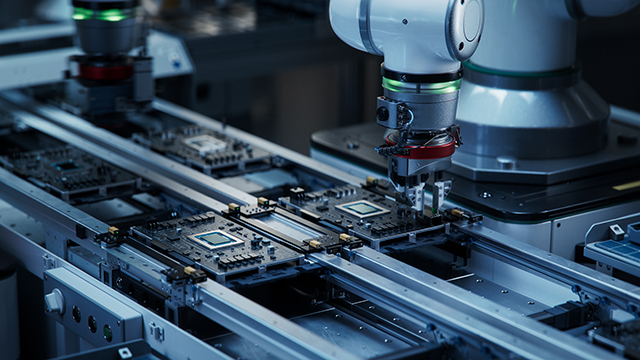

Questa Logic Verification, part of the Questa One smart verification solution, delivers a transformative shift to AI-powered verification, pioneering intelligent automation for ASIC, SoC, and FPGA designs. The platform emphasizes breaking traditional verification bottlenecks through unmatched speed, efficiency, and scalability.

Questa One encompasses smart creation, smart analysis, smart debug, smart regression, and smart engines across a comprehensive suite of tools, enabling engineers to achieve higher coverage closure faster while reducing overall verification effort.

Explores smart verification capabilities encompassing smart creation, smart analysis, smart debug, smart regression, and smart engines, leveraging AI and machine learning to accelerate the entire verification flow.

Accelerate product lifecycle and lower DFT sign-off costs with scalable, streamlined, context-aware DFT technology offering industry-leading performance for complex SoC and chiplet designs.

Smart systems require failure detection and control. Questa One tools perform safety analysis and fault simulation with safety mechanisms for safety-critical automotive, industrial, and medical applications.

High-performance simulation tools spanning register-transfer level, gate-level, design-for-test, and fault simulations across all abstraction levels, delivering the fastest engines for SoC and FPGA verification.