- info@advinno.com

- Mon - Fri: 9.00 am - 6.00 pm

We are creative, ambitious and ready for challenges! Hire Us

We are creative, ambitious and ready for challenges! Hire Us

We have 20+ years of experience in delivering superior and innovative products

22, Sin Ming Lane, #05-75 Midview City Singapore 573969

info@advinno.com

(+65) 6777-2240 / 6570 6086

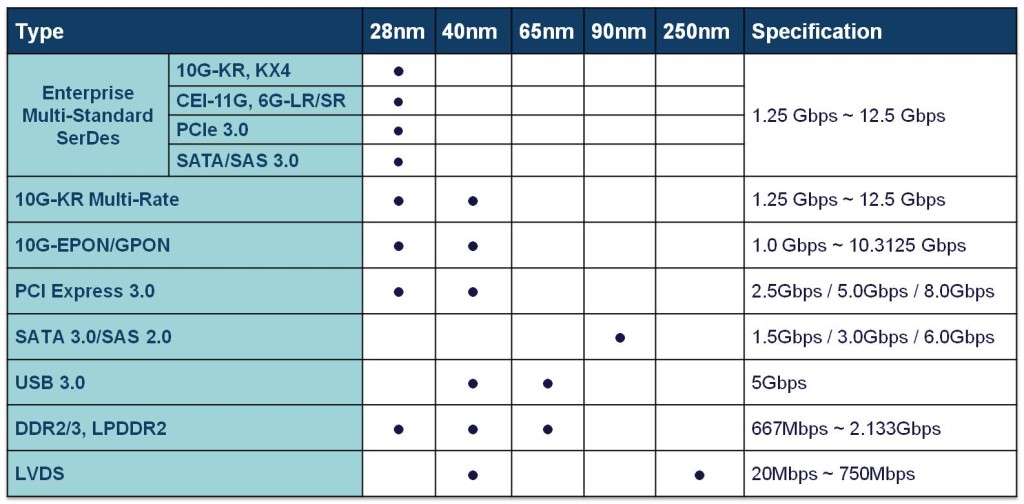

Advinno’s silicon-proven IP provides designers with a broad range of synthesizable implementation IP, hardened PHYs and verification IP for ASIC, FPGA, and SoC designs. The Advinno in-house IP portfolio includes bus interface, mixed signal, data converter, multimedia, power management, and SERDES.

These IPs are silicon and production proven in the ASIC projects of a global customer base.

Advinno’s wide experience with all kinds of IP combined with a comprehensive customization flexibility allows customers to quickly meet both product requirements and to achieve market goals at the same time. Advinno has an established reputation in integrating a wide range of IP supported by a full suite of design services and an experienced technical team dedicated to developing design flows that address the complexities of today’s ASIC designs.