- info@advinno.com

- Mon - Fri: 9.00 am - 6.00 pm

We are creative, ambitious and ready for challenges! Hire Us

We are creative, ambitious and ready for challenges! Hire Us

We have 20+ years of experience in delivering superior and innovative products

22, Sin Ming Lane, #05-75 Midview City Singapore 573969

info@advinno.com

(+65) 6777-2240 / 6570 6086

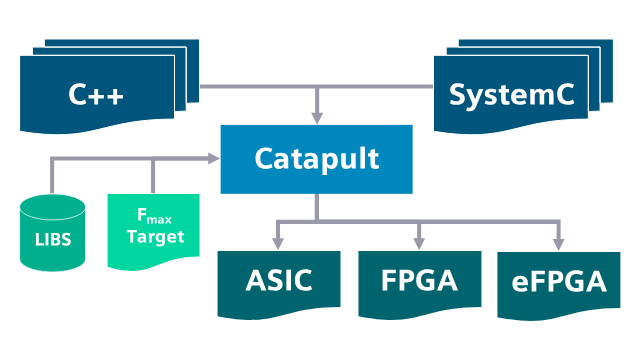

Catapult has the broadest portfolio of hardware design solutions for C++ and SystemC-based High-Level Synthesis (HLS). Catapult’s physically-aware, multi-VT mode, with Low-Power estimation and optimization, plus a range of leading Verification solutions make Catapult HLS more than just "C to RTL".

The past several years have seen an explosion in the adoption of HLS for chip design driven by increasing design and verification complexity as well as time to market pressures. Catapult HLS enables designers to get their chips to market faster by shortening the overall design and verification flow.

A comprehensive HLS flow taking C++ or SystemC as the design input and optimally targeting ASIC, eFPGA or FPGA implementations tuned for frequency and target technology.

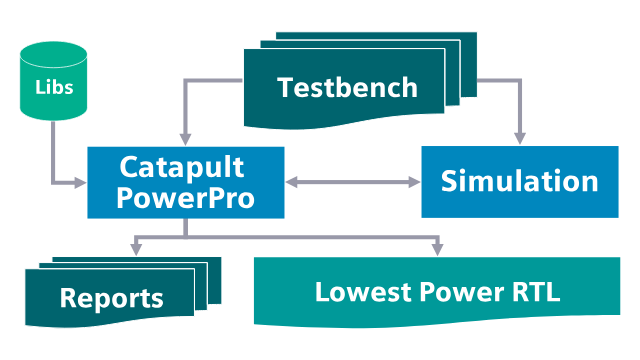

When it comes to early design space exploration, power estimation, and optimizing for low-power ASIC RTL, Catapult generates highly efficient RTL that is optimized with our PowerPro technology under the hood.

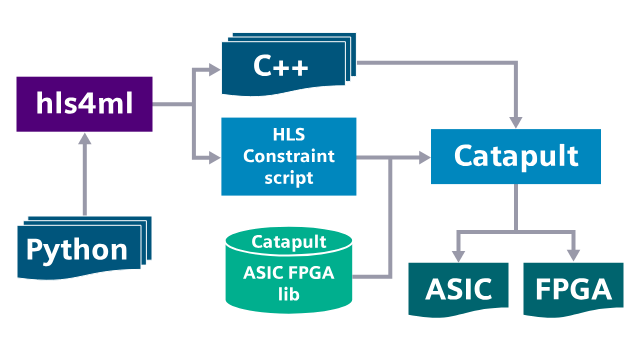

Catapult AI enhances HLS for accelerated design exploration, quantization analysis and performance, power and area prediction.

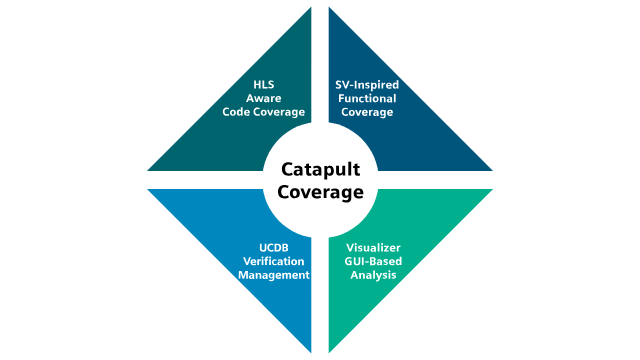

Accelerate your High-Level Verification (HLV) flow with known and trusted methods using the Catapult HLV Platform. Reduce your overall SoC verification turnaround time and costs by up to 80% leveraging High-Level Design Checking, Code/Functional Coverage, and static plus formal methods.

HLS-aware code coverage including support for statement, branch, condition, expression (FEC) and array access coverage plus SystemVerilog-inspired functional coverage with support for covergroups, coverpoints, bins and crosses.

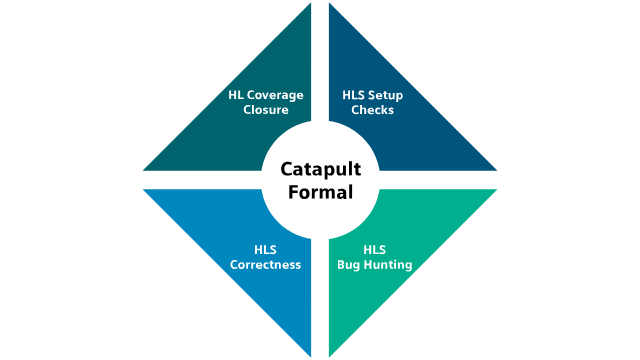

Formally find mistakes, ambiguities and problem design issues or user constraint mistakes early in the HLS process. Even with differences in timing, and interfaces, Catapult Formal enables verification and a coverage closure flow.

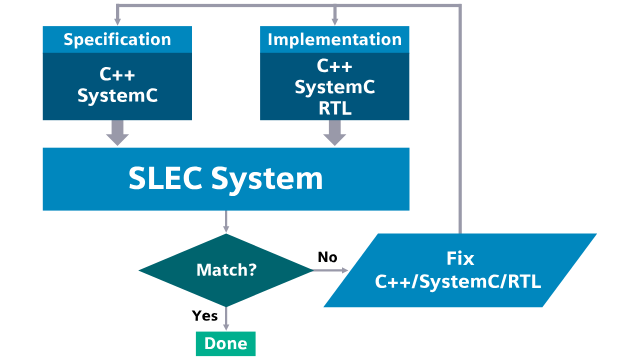

Check the correctness of RTL against your High-Level models using SLEC. Enabling proof that specification and implementation are identical despite differences in language, timing, or abstraction.

High-level design verification with Questa HL-SYC expansion helps eliminate issues before synthesis by starting verification earlier in the flow.