- info@advinno.com

- 周一至周五:上午 9:00 至下午 6:00

Aprisa Place & Route

- Home

- 产品

- Uncategorized

- Aprisa Place & Route

Aprisa Place and Route

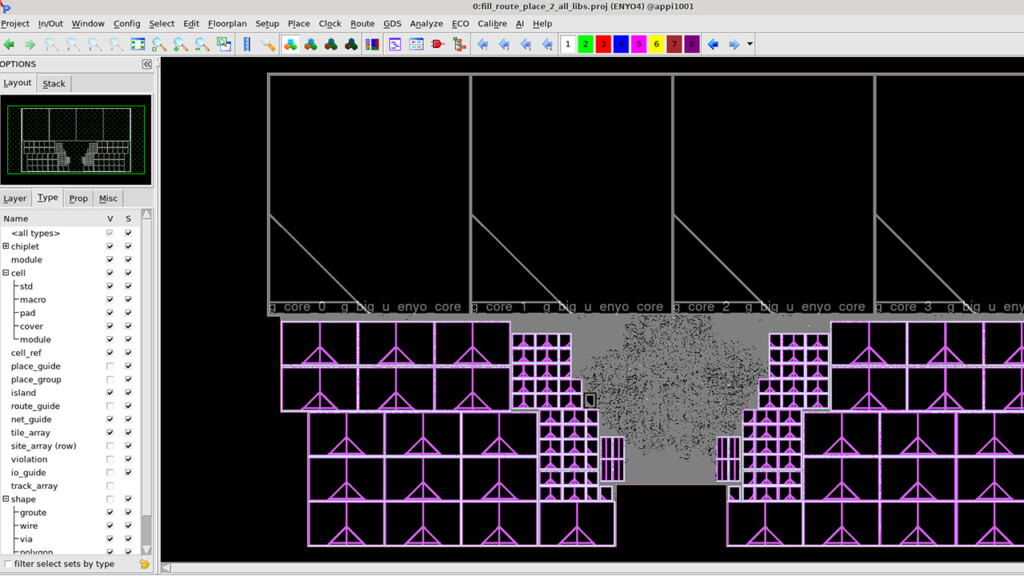

Aprisa is Siemens EDA’s complete RTL-to-GDS digital implementation solution designed for advanced process nodes. It addresses chip complexity, schedule pressure, and development costs through faster design closure and more predictable PPA with a detail-route-centric architecture.

Built with AI at its core, Aprisa delivers a 10x productivity boost for designers through machine learning and reinforcement learning for design exploration, generative AI for tool assistance, and AI agents for design tasks, enabling timing closure in days rather than weeks for complex SoC designs.

Key Aprisa Solutions:

- RTL-to-GDS digital implementation

- AI-powered design automation

- Detail-route-centric architecture

- Unified hierarchical data model

- 10x productivity boost with AI

- PowerFirst power-centric mode

- 3x more efficient computing

- Signoff correlation for timing and DRC

Aprisa AI

Built-in AI-powered technology extending Siemens’ industrial-grade AI capabilities throughout the implementation flow, including generative AI for tool assistance, AI agents for design tasks, and ML/RL for design space exploration.

- Generative AI assist and workflow automation

- AI agents for design task execution

- ML/RL for design space exploration

- 10% better design PPA results

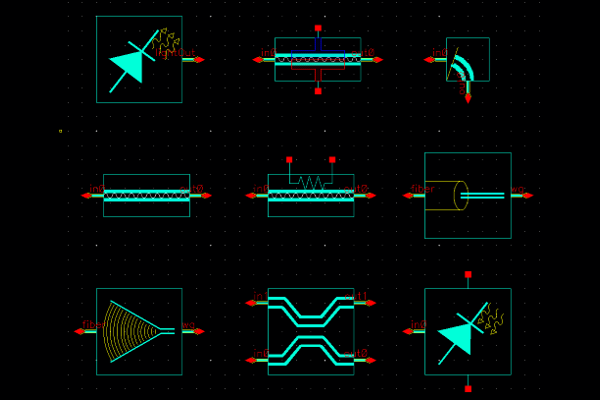

Aprisa RTL-to-GDS

Complete RTL-to-GDS solution providing faster, more predictable PPA closure and better power results for power-centric designs, leveraging a detail-route-centric architecture with shared foundation engines.

- Faster and more predictable PPA closure

- Detail-route-centric architecture

- Shared foundation engines across synthesis to routing

- In-hierarchy optimization (iHO) for top and block levels

Advanced Routing and Closure

Advanced routing technology with PowerFirst mode enabling power-first implementation, signoff tool correlation for STA timing and DRC, and significantly reduced ECO iterations that compress timing closure from weeks to days.

- PowerFirst mode for power-centric implementation

- Signoff-correlated STA timing and DRC

- Reduced ECO iterations

- Timing closure effort compressed from weeks to days