- info@advinno.com

- 周一至周五:上午 9:00 至下午 6:00

Oasys-RTL 逻辑综合

- Home

- 产品

- Uncategorized

- Oasys-RTL 逻辑综合

Oasys-RTL 逻辑综合

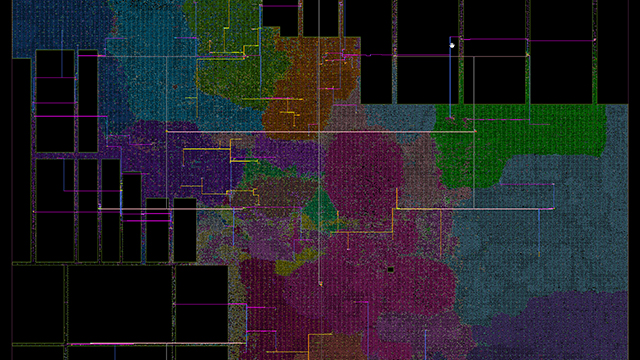

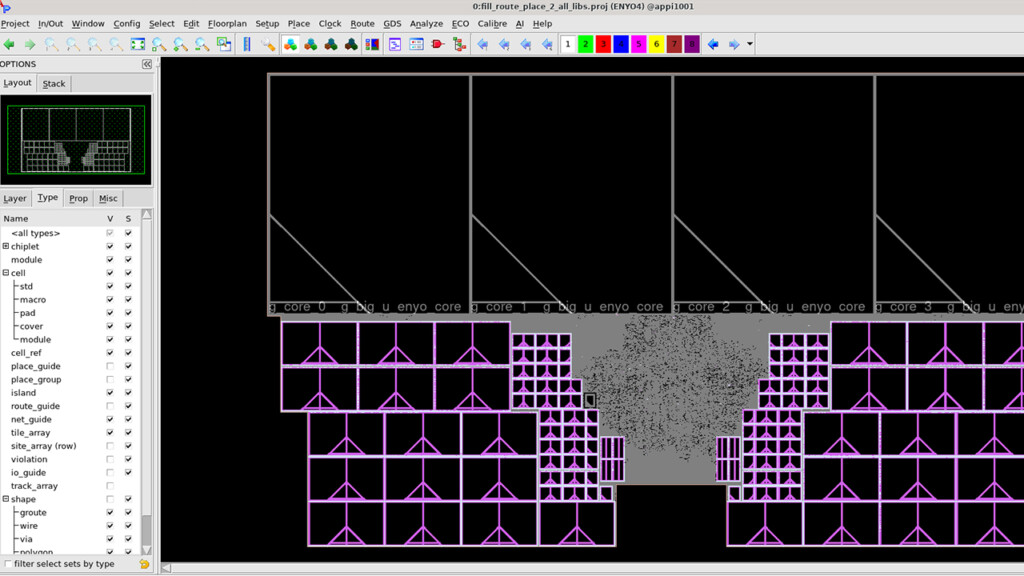

Oasys-RTL Logic Synthesis, now integrated into the Aprisa digital implementation platform, delivers physically-aware RTL synthesis optimized for advanced process nodes. The solution provides faster design closure and more predictable power, performance, and area (PPA) results through a detail-route-centric architecture.

Leveraging AI and machine learning at every stage, Oasys-RTL synthesis offers a 10x productivity boost for designers through ML/RL exploration, generative AI for tool assistance, and AI agents for design tasks, enabling timing closure in days rather than weeks.

Key Oasys-RTL Logic Synthesis Solutions:

- Physically-aware RTL synthesis

- Faster, predictable PPA closure

- AI-powered synthesis automation

- In-hierarchy optimization (iHO)

- Power-first implementation mode

- Signoff tool correlation for STA and DRC

- Timing closure in days not weeks

- Shared foundation with P&R engines

RTL-to-GDS Logic Synthesis

Complete RTL-to-GDS synthesis providing faster, more predictable PPA closure and better power results for power-centric designs, with a unified hierarchical data model shared across synthesis, placement, CTS, and routing.

- Faster and more predictable PPA closure

- Unified hierarchical data model

- Shared foundation engines across synthesis and P&R

- In-hierarchy optimization (iHO) for top and block levels

AI-Powered Synthesis

Built-in AI-powered technology extends Siemens industrial-grade AI capabilities into logic synthesis, including generative AI for tool assistance, AI agents for design task automation, and ML/RL for design space exploration.

- 10x productivity boost via ML/RL exploration

- Generative AI for tool assistance

- AI agents for design task automation

- 10% better design PPA results

Power-First Synthesis

PowerFirst mode enables power-first implementation by converging on power objectives before performance, delivering highly efficient RTL synthesis for power-centric SoC designs targeting AI/ML, mobile, and IoT applications.

- PowerFirst mode for power-centric designs

- Power optimization before performance convergence

- Reduced ECO iterations

- Signoff-correlated timing and DRC results