- info@advinno.com

- 周一至周五:上午 9:00 至下午 6:00

坦纳定制IC

- Home

- 产品

- Uncategorized

- 坦纳定制IC

坦纳定制IC

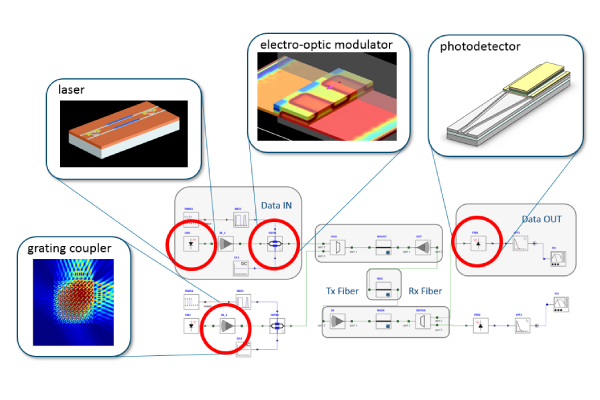

Tanner Custom IC provides a complete analog mixed-signal design flow covering design capture, simulation setup, launch, and results analysis verification. The S-Edit schematic capture environment handles complex full-custom designs with native OpenAccess support and connections to over 180 PDKs from more than 30 foundries.

Designed for analog and mixed-signal IC designers, the Tanner Custom IC environment streamlines the full design cycle from schematic entry through simulation and layout, with deep integration to Eldo and AFS simulators and tight cross-probing across all design views.

Key Tanner Custom IC Solutions:

- Native OpenAccess support

- Multiple-view cell support (SPICE, Verilog, layout)

- Schematic-driven layout acceleration

- 180+ PDKs from 30+ foundries

- Advanced array and bus handling

- Cross-probe between schematic, layout, and LVS

- Multi-testbench simulation management

- Sweep, corner, and Monte Carlo analysis

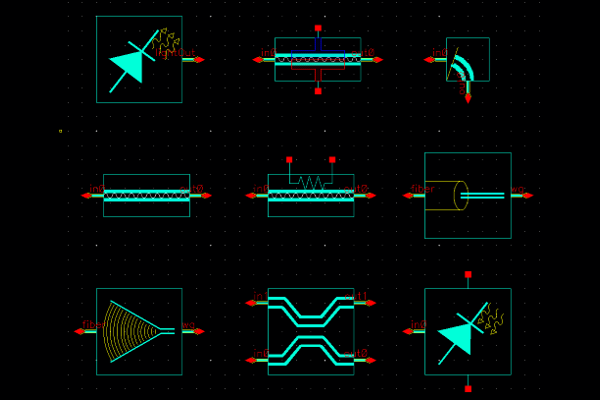

Custom IC Design Capture

The S-Edit schematic capture environment handles complex full-custom designs with native OpenAccess support, multiple-view cell management, and schematic-driven layout acceleration, all connected to leading foundry PDKs.

- Native OpenAccess support

- Multiple-view cell support (SPICE, Verilog, layout, Verilog-A/AMS)

- Schematic-driven layout acceleration

- TCL/Tk scripting support

Schematic Design Environment

Advanced schematic capture with configurable Electrical Rule Checks, schematic comparison with visual diff, cross-probe functionality between schematic, layout, and LVS reports, and full revision control integration.

- Advanced array and bus handling

- Schematic comparison with visual diff display

- Cross-probe between schematic, layout, and LVS

- Configurable Electrical Rule Checks (ERC)

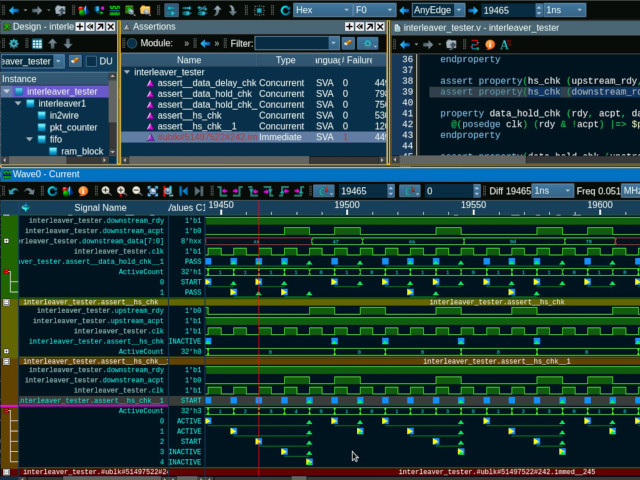

Simulation Management

Integrated simulation management with real-time pass/fail status tracking, back annotation of DC/AC parameters to schematics, and support for sweep, corner, and Monte Carlo analysis setup across multiple testbenches.

- Real-time pass/fail status tracking

- Back annotation of DC/AC parameters to schematics

- Sweep, corner, and Monte Carlo analysis setup

- Project-wide measurement aggregation